指令周期

定义

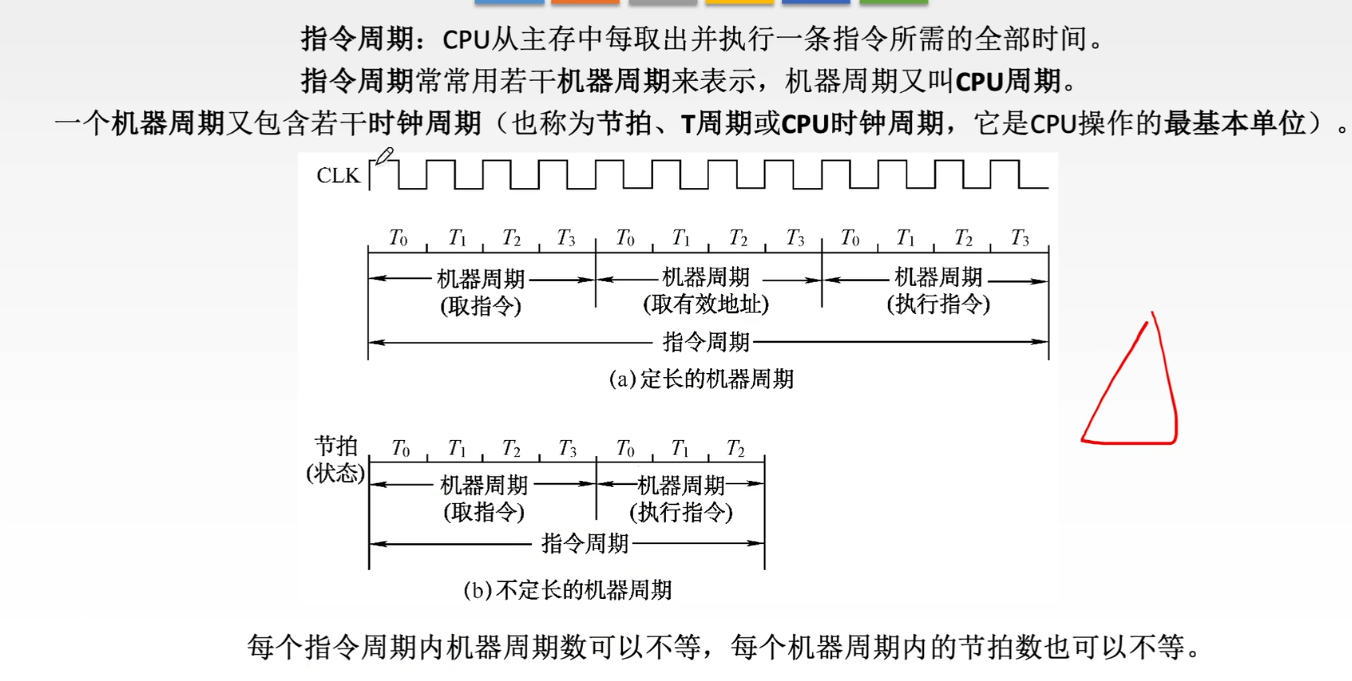

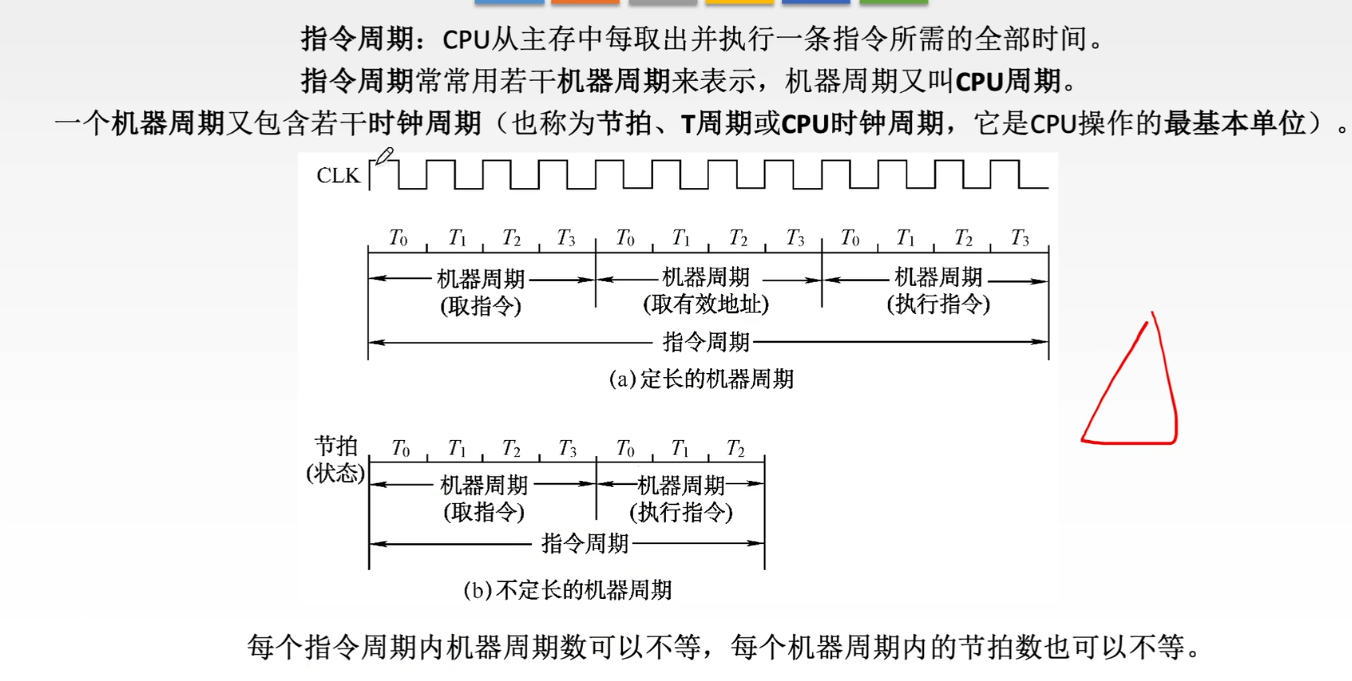

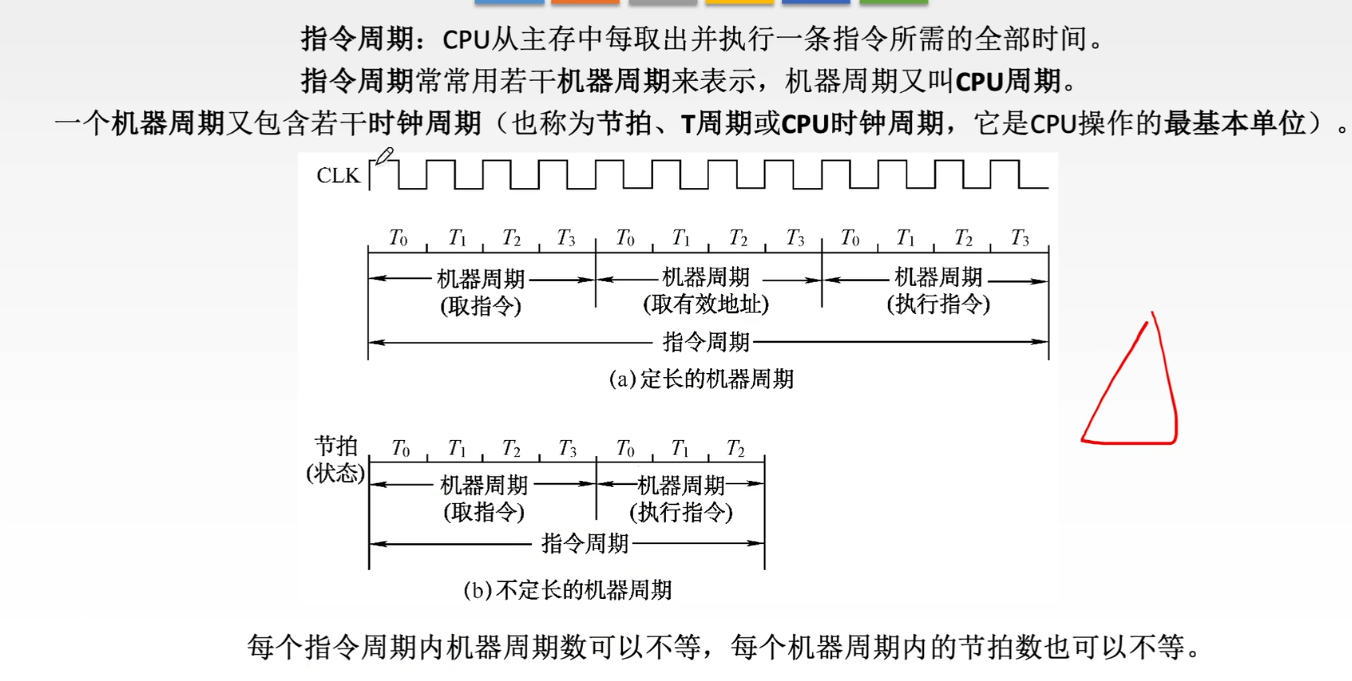

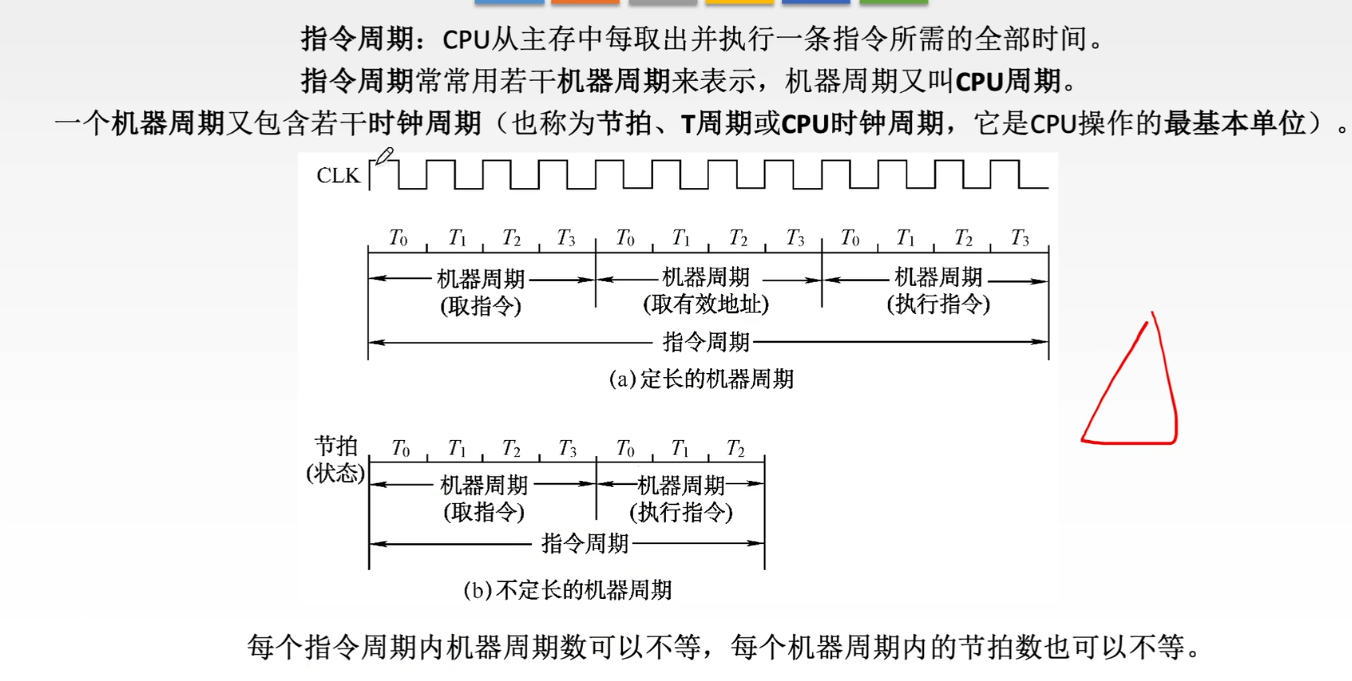

指令周期是计算机执行一条指令所经历的整个过程,从取出指令到完成指令执行,包括所有的步骤和阶段。每条指令的执行都需要经历若干个固定的步骤,这些步骤构成了指令周期。

组成部分

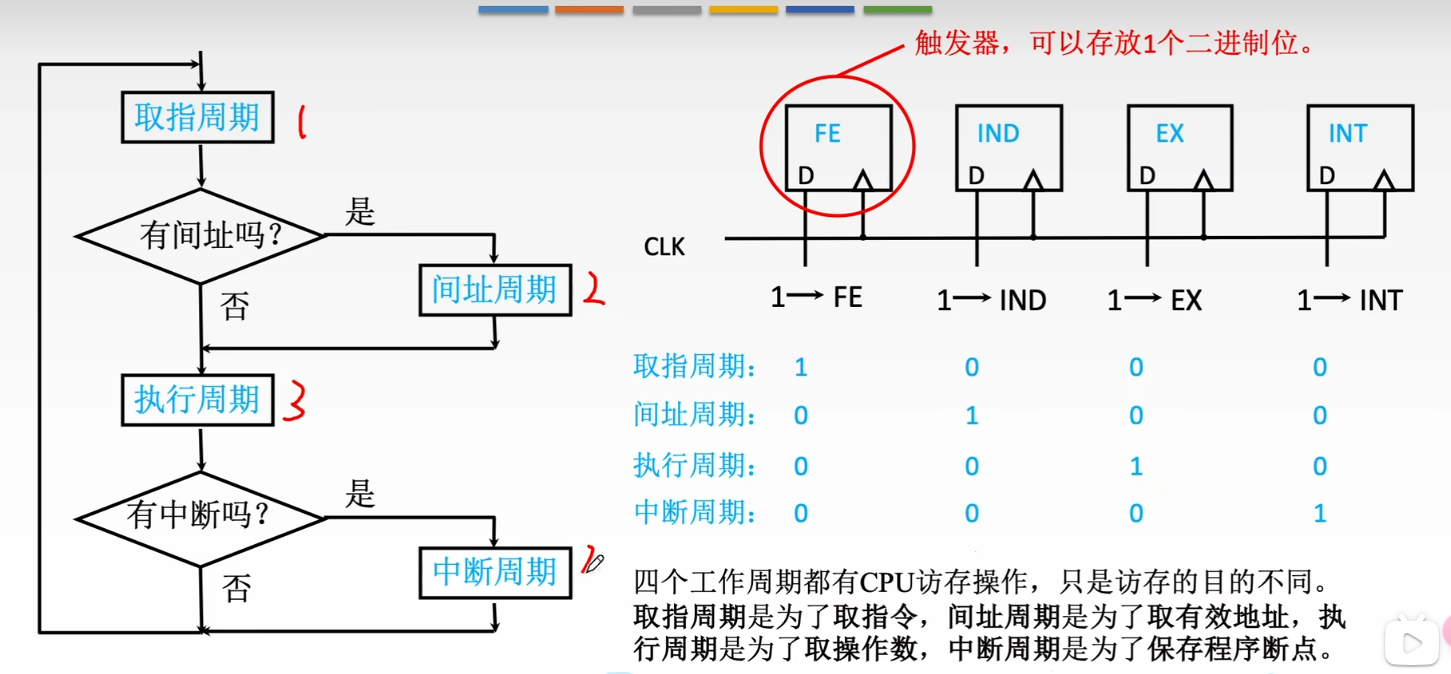

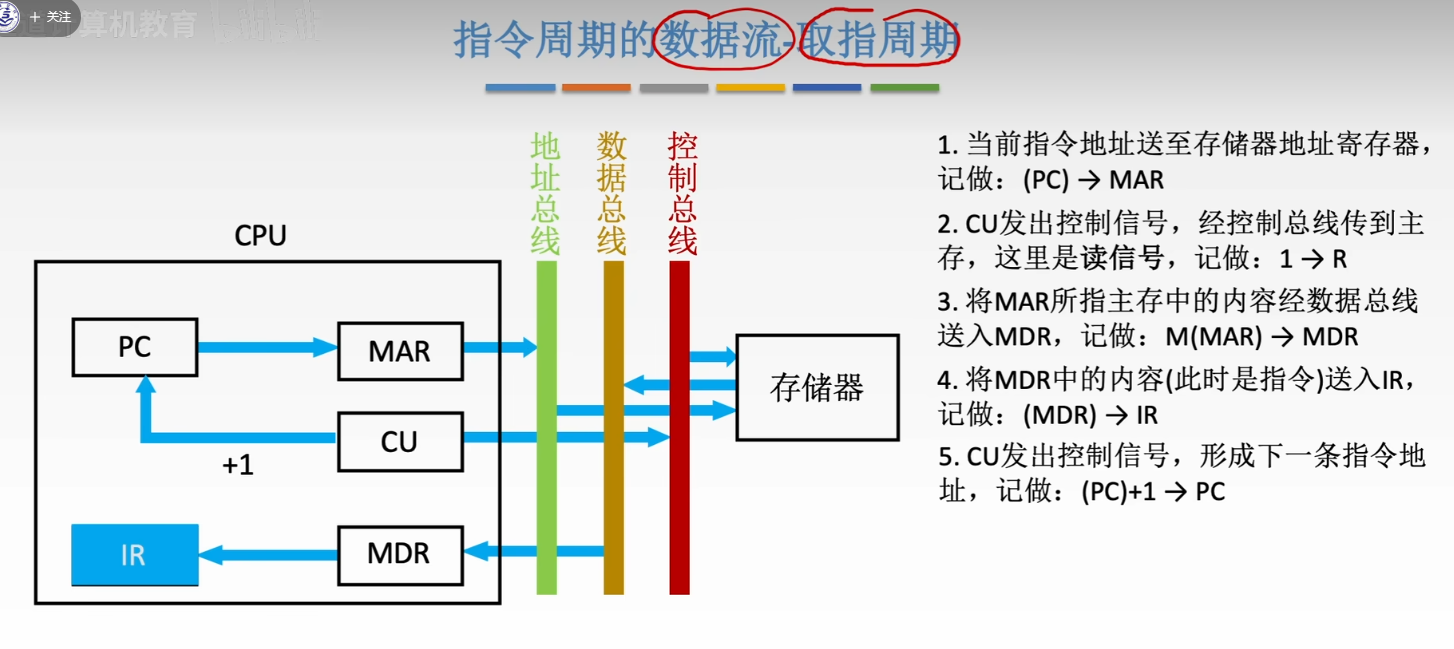

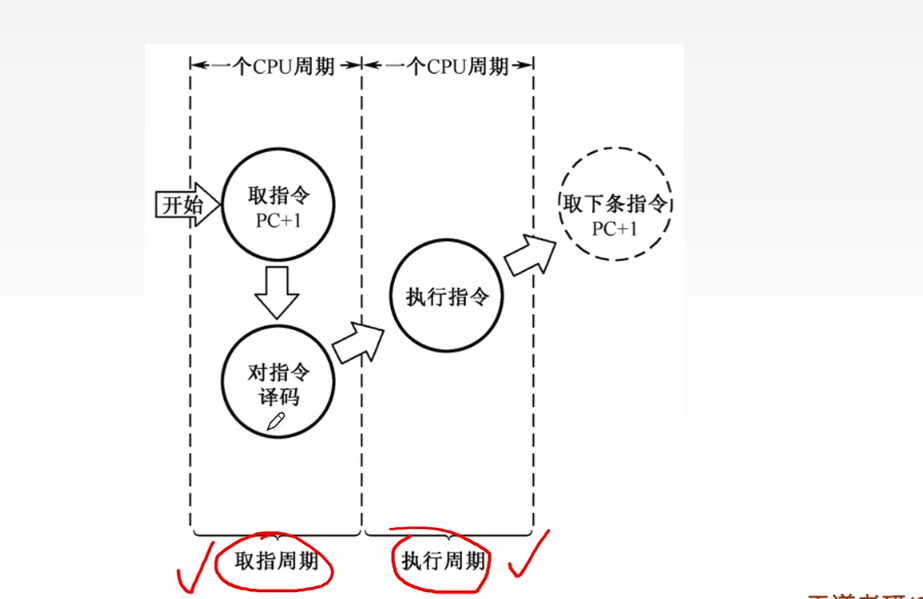

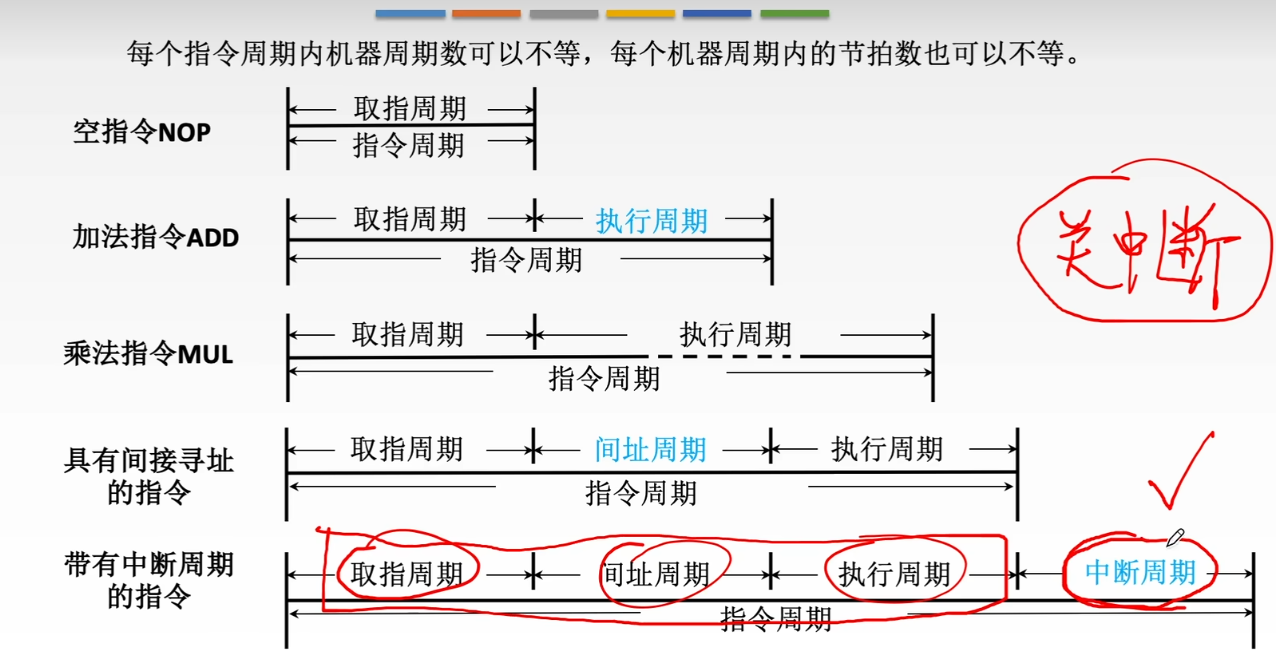

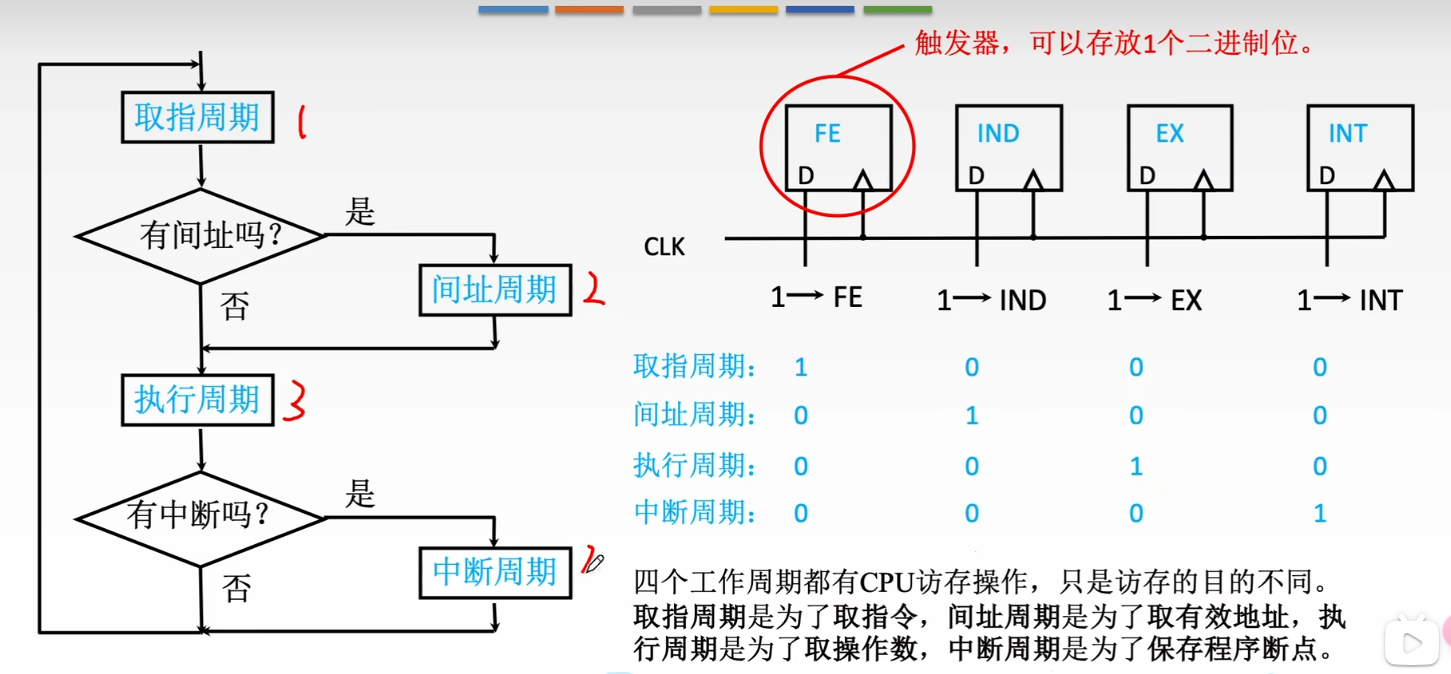

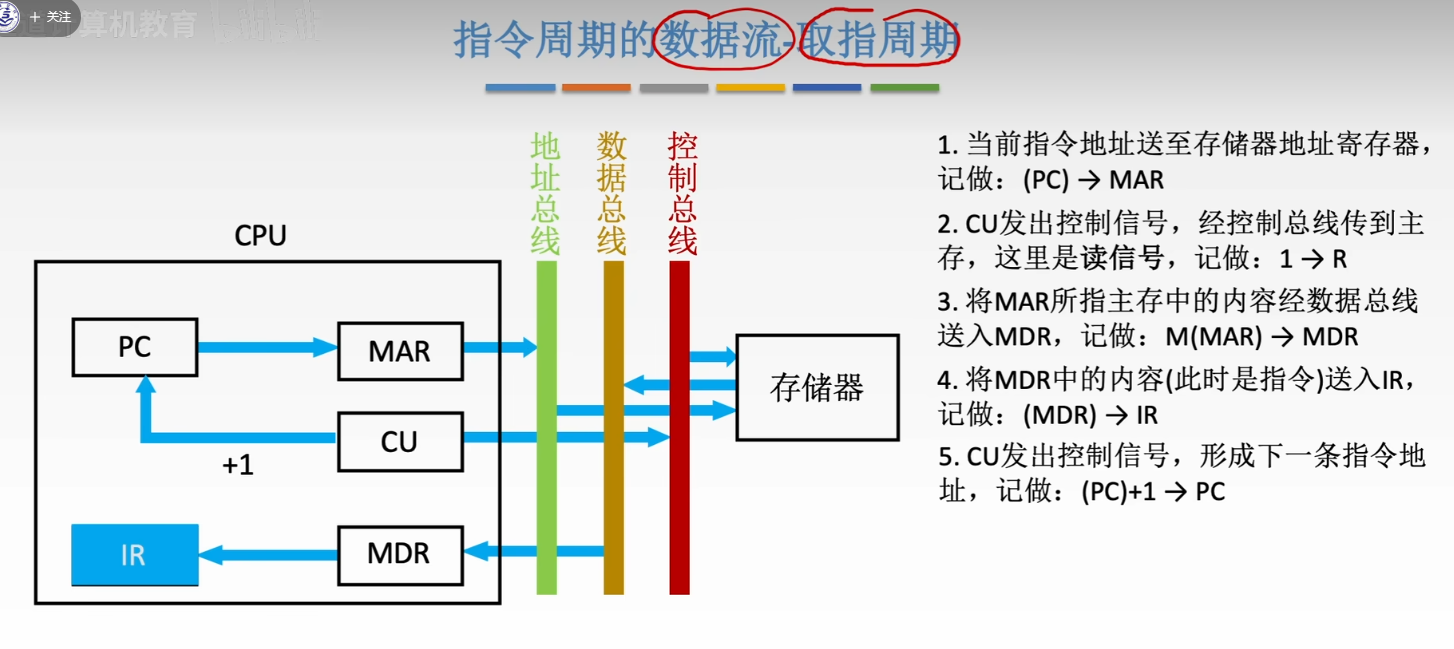

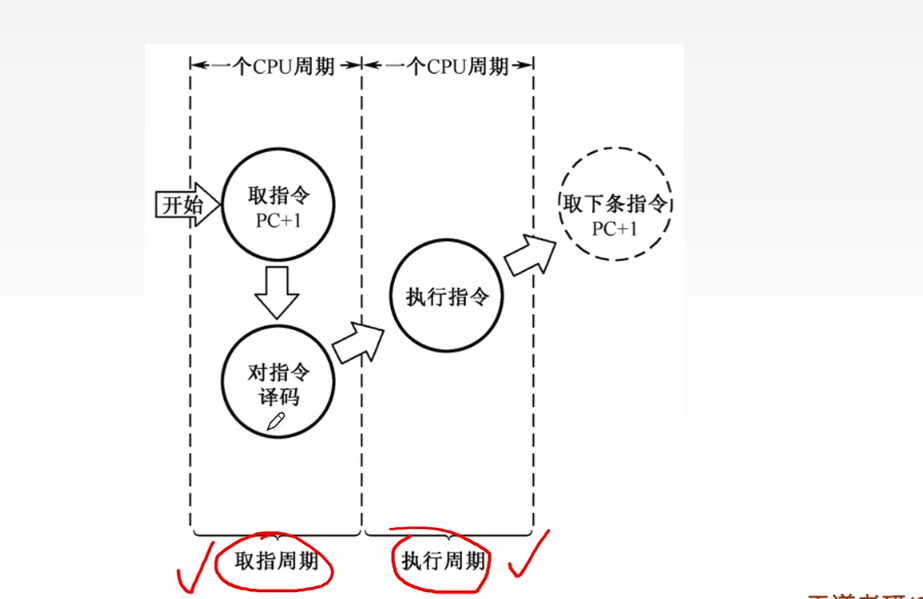

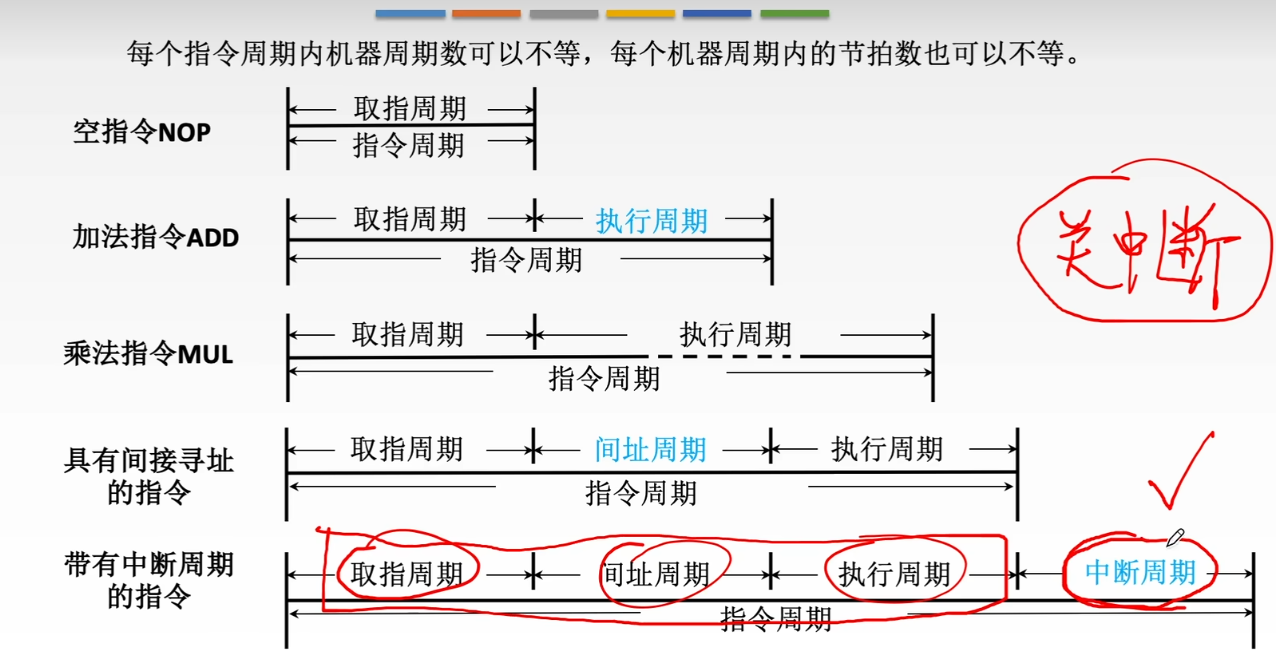

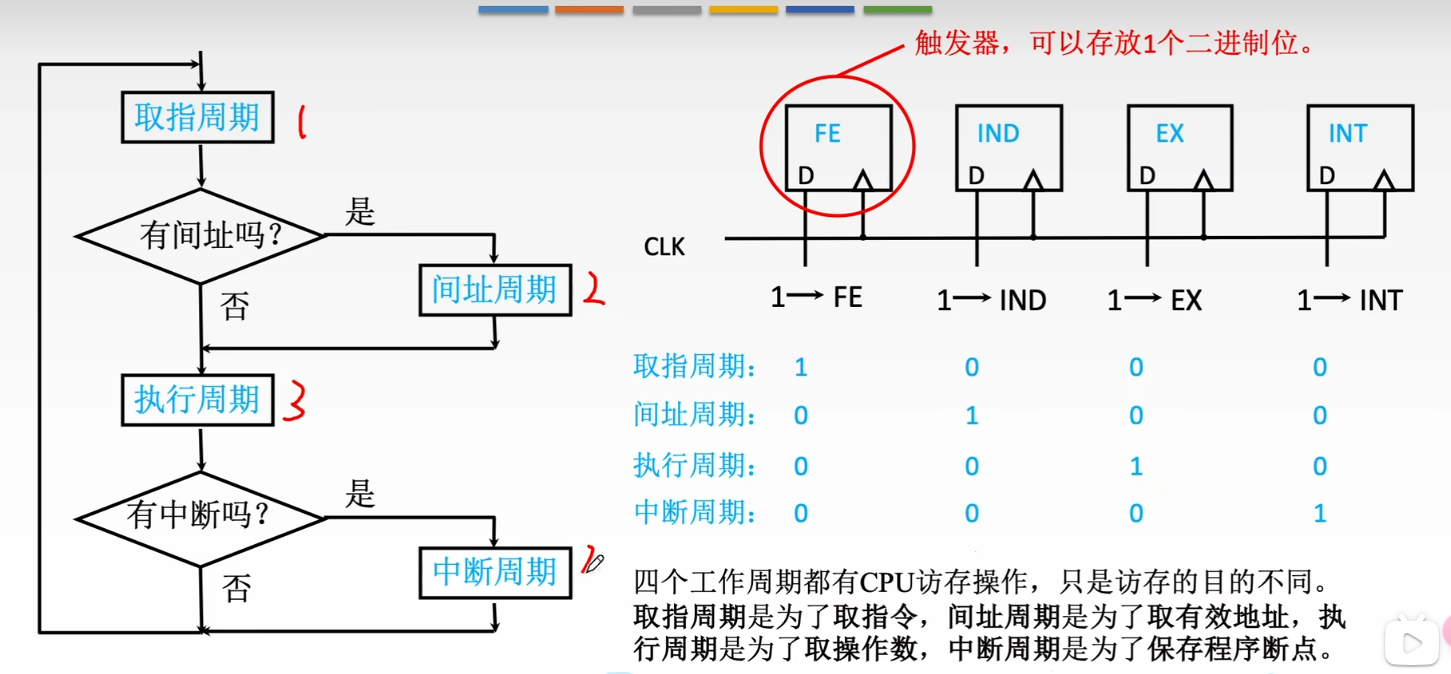

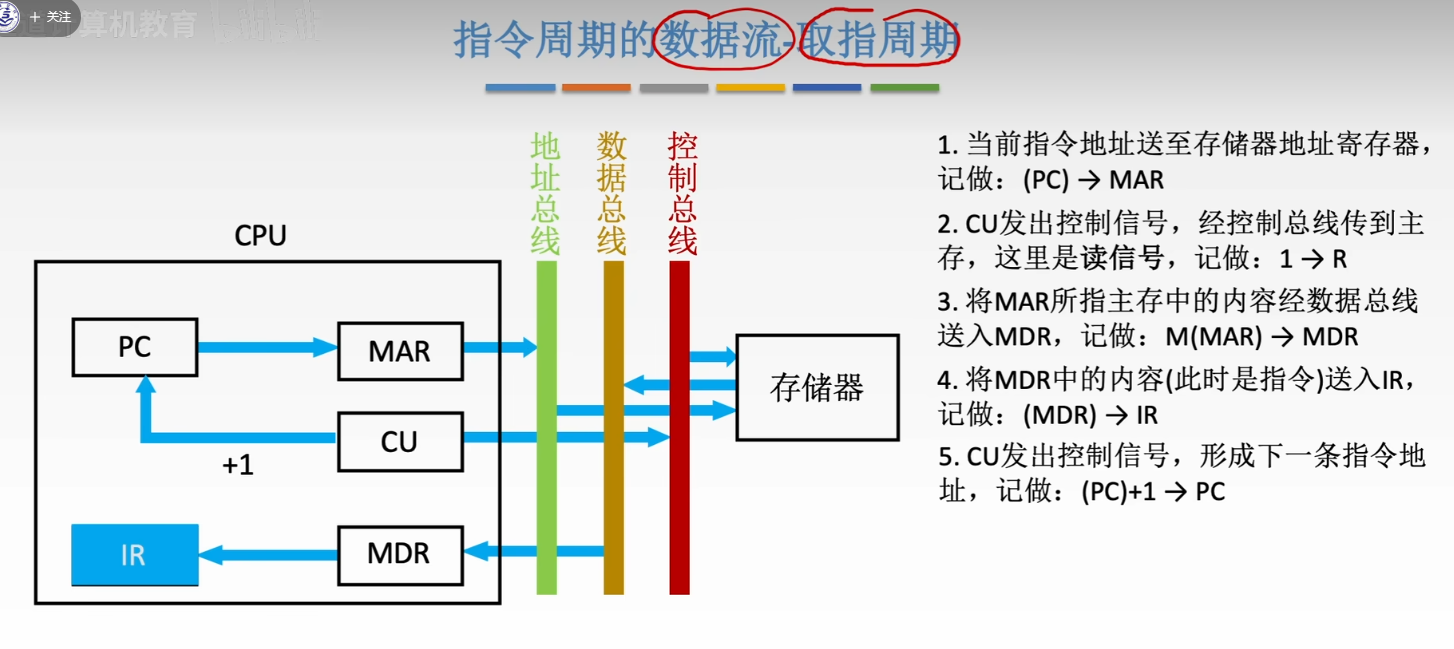

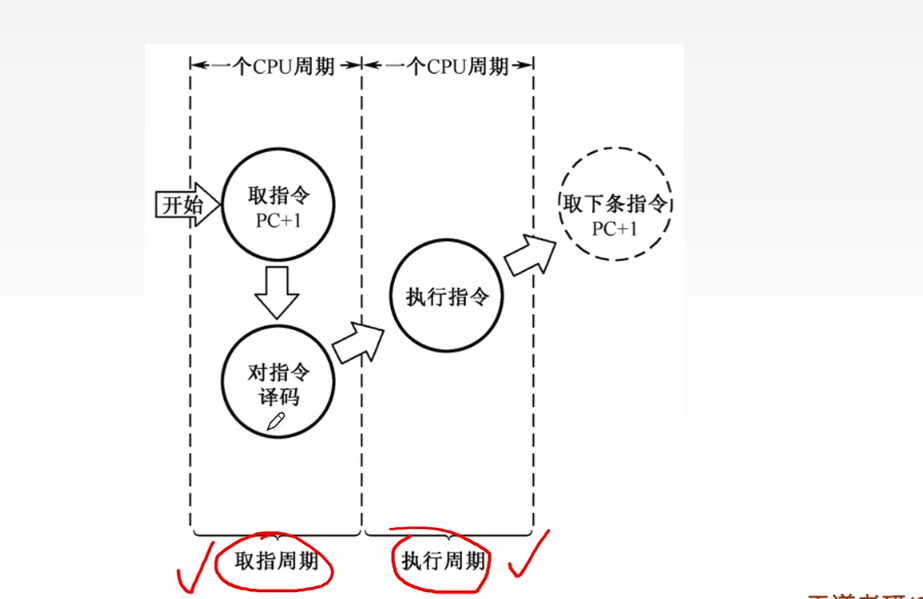

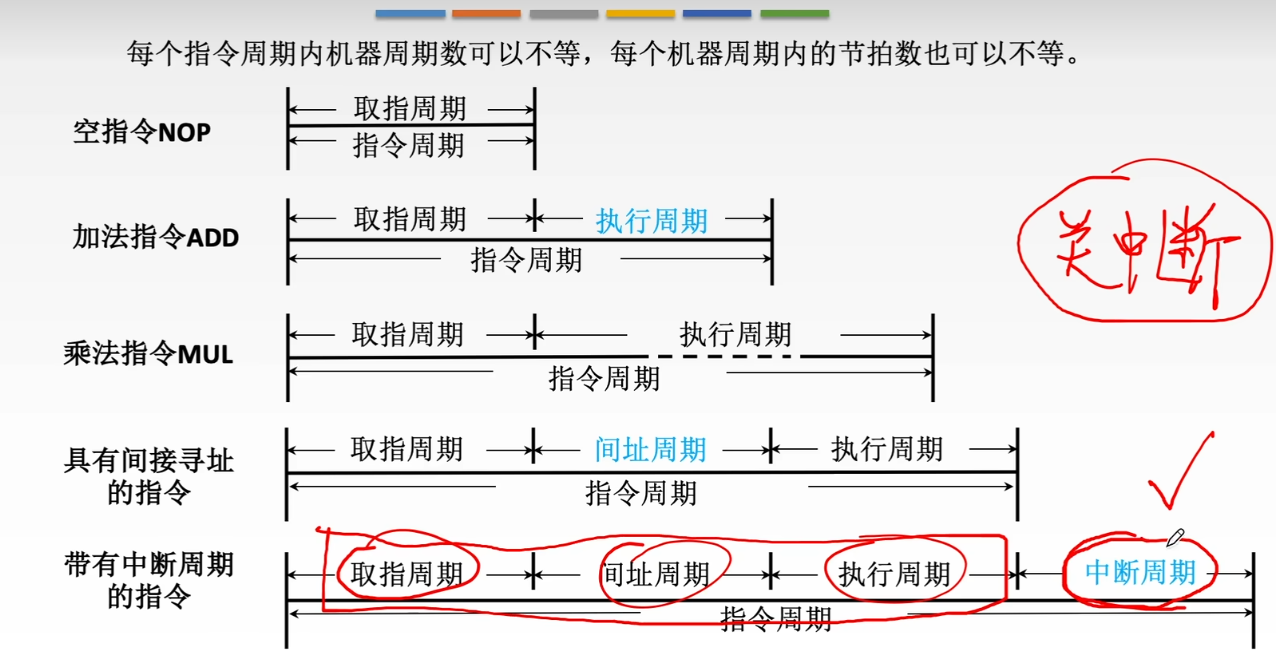

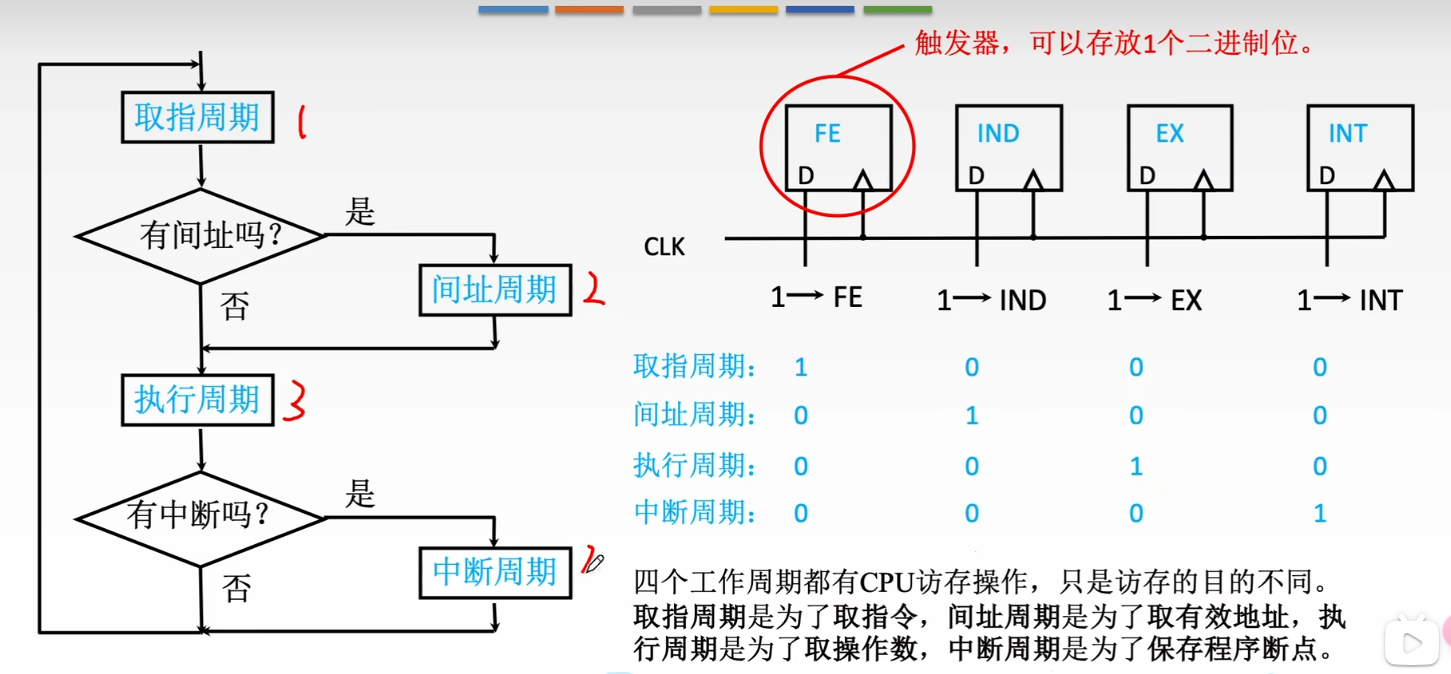

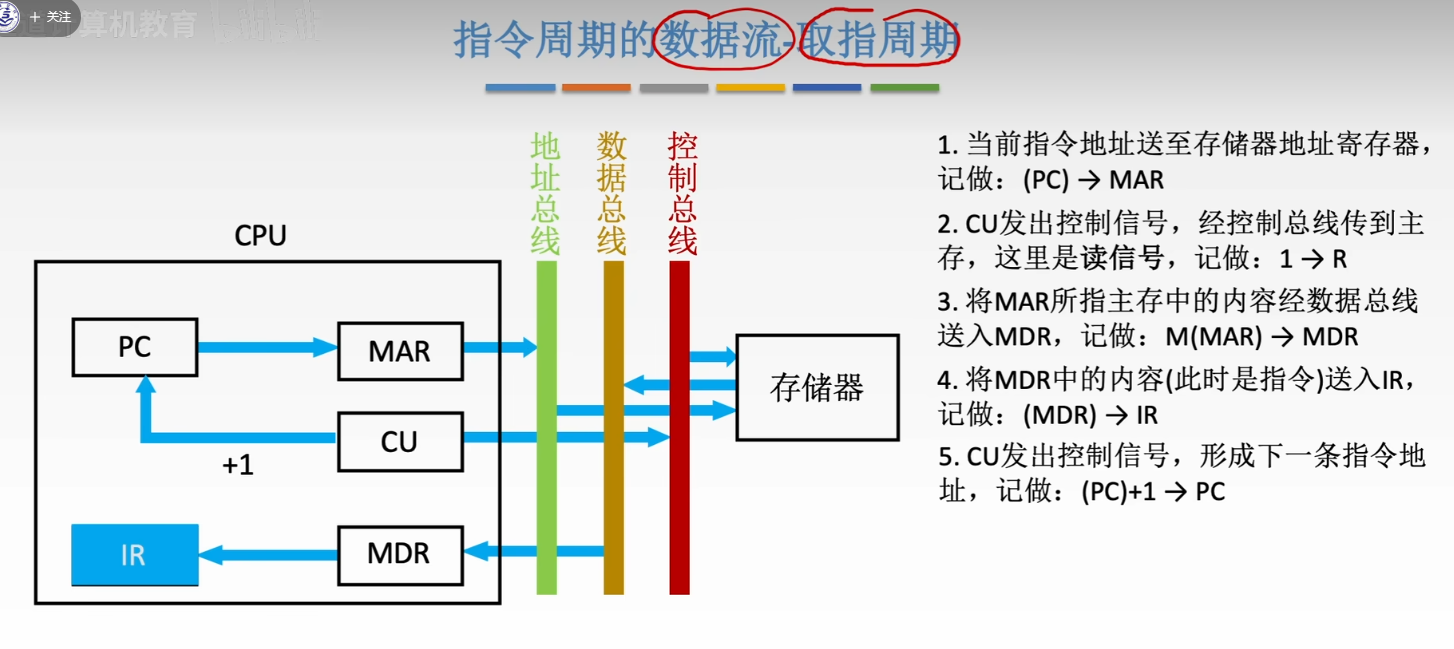

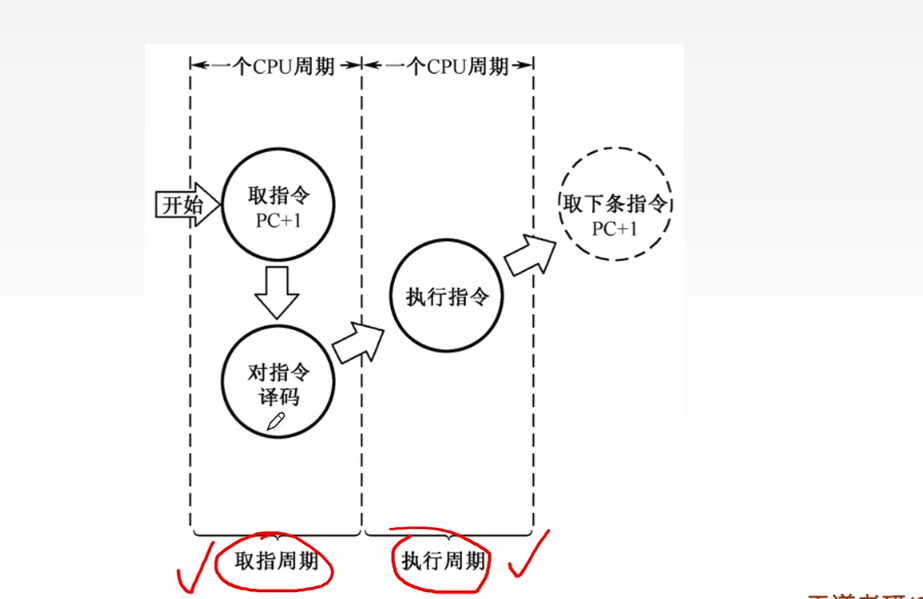

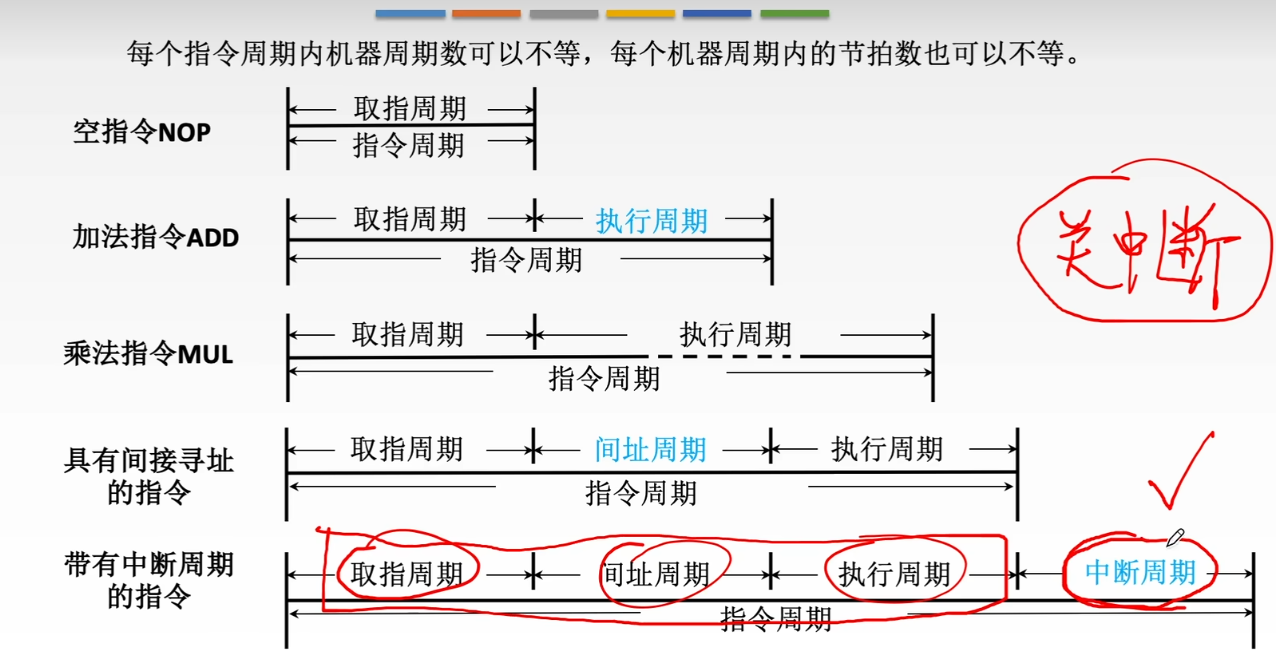

1.取指周期(Fetch Cycle)

从内存中取出指令。

2.译码周期(Decode Cycle)

将取出的指令译码,以确定操作类型和操作数。

3.间址周期(Indirect Cycle)

如果指令使用间接地址方式,需要访问内存获取实际操作数地址。

4.执行周期(Execute Cycle)

执行指令所规定的操作。

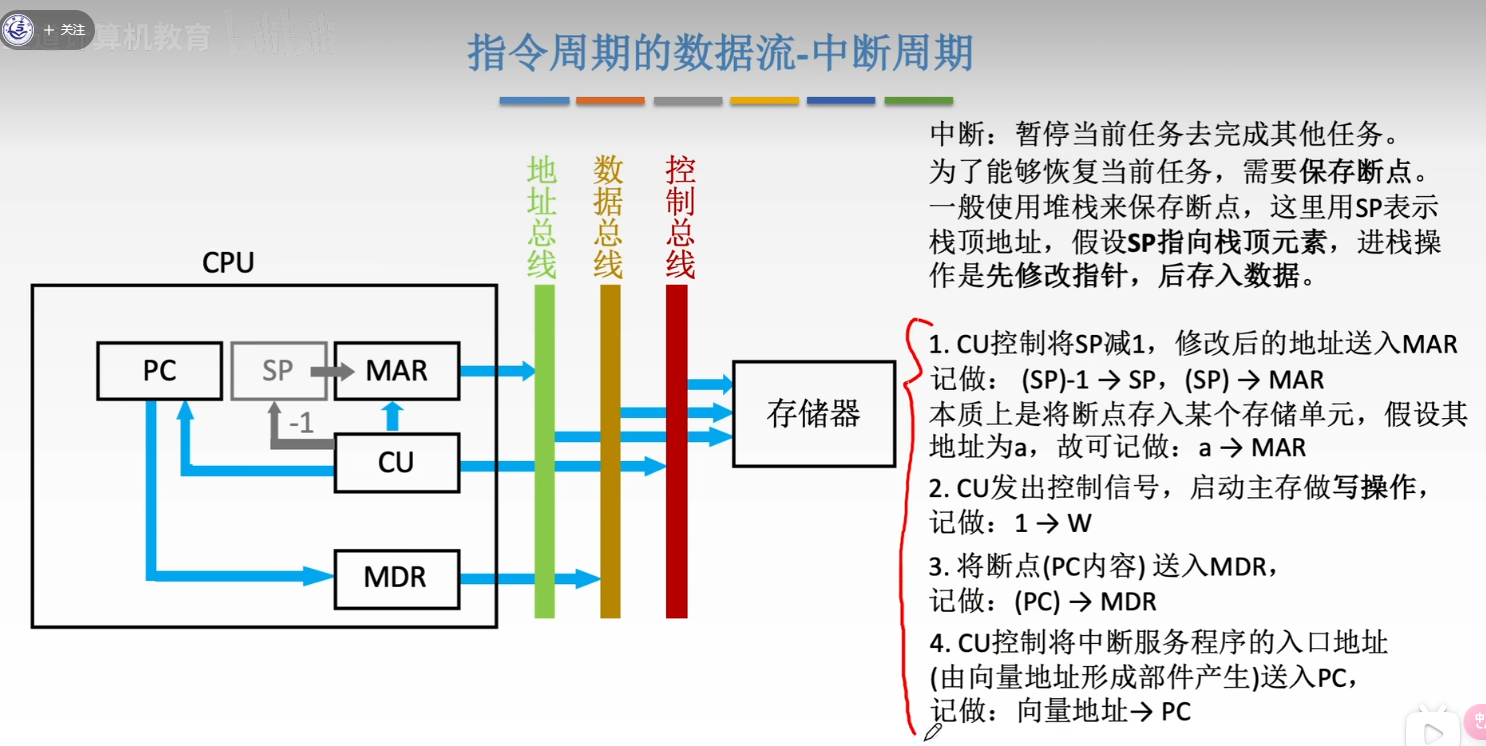

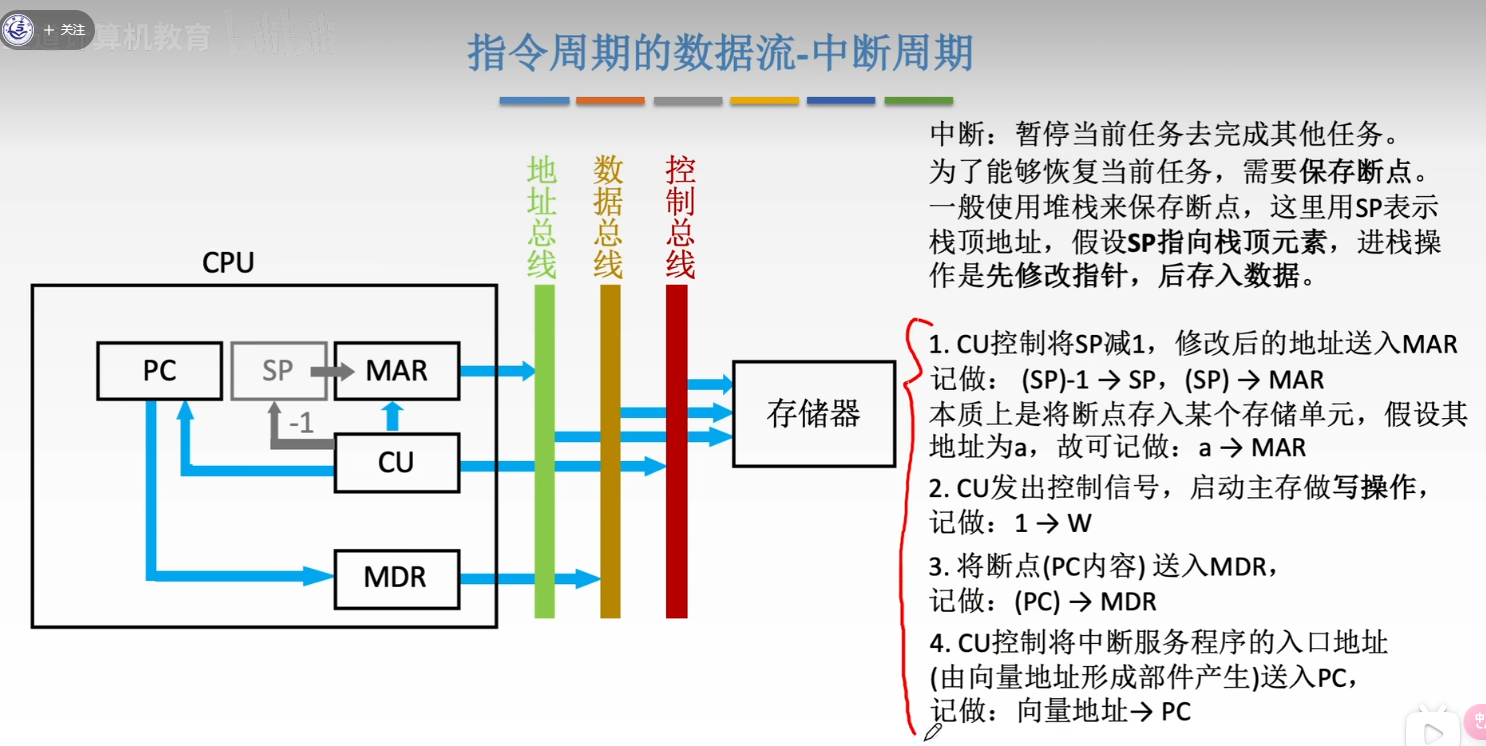

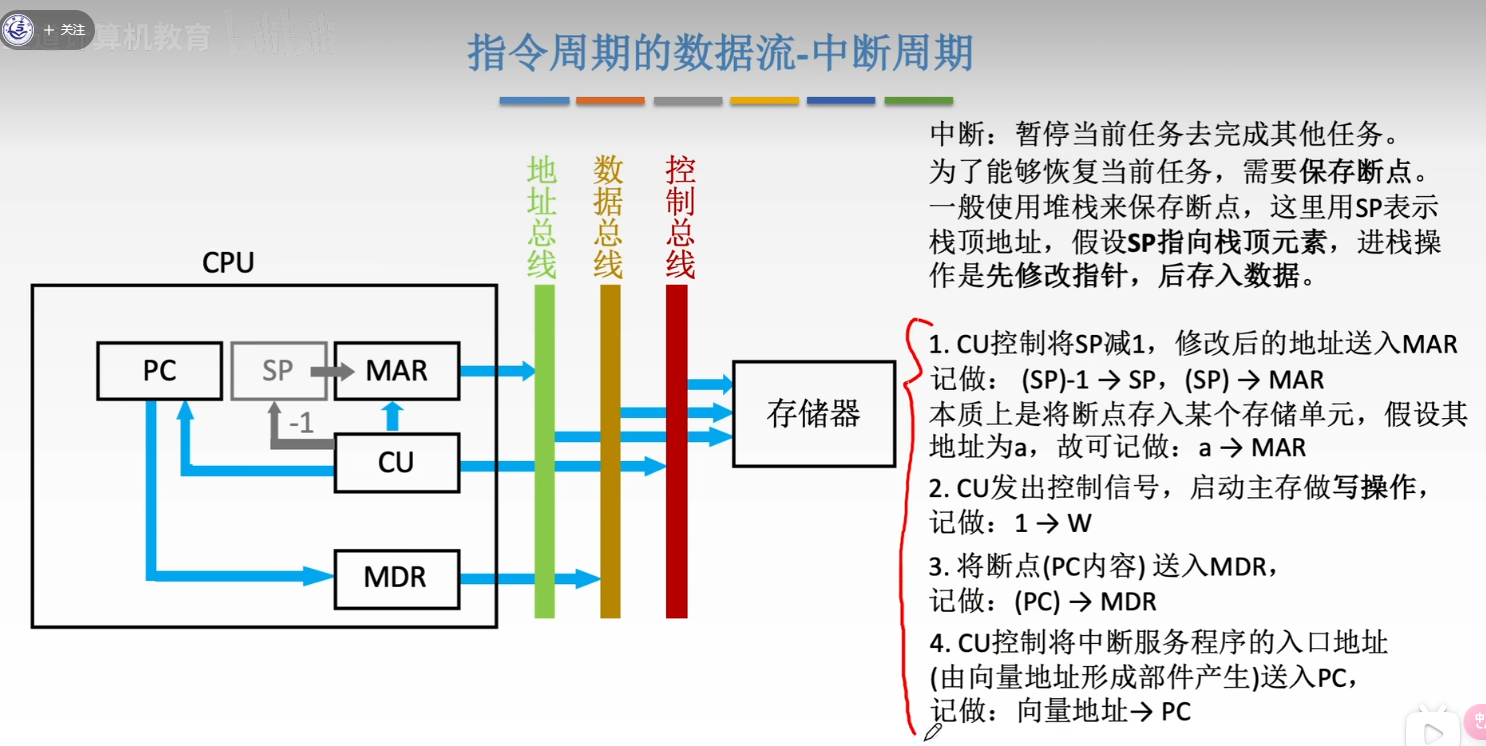

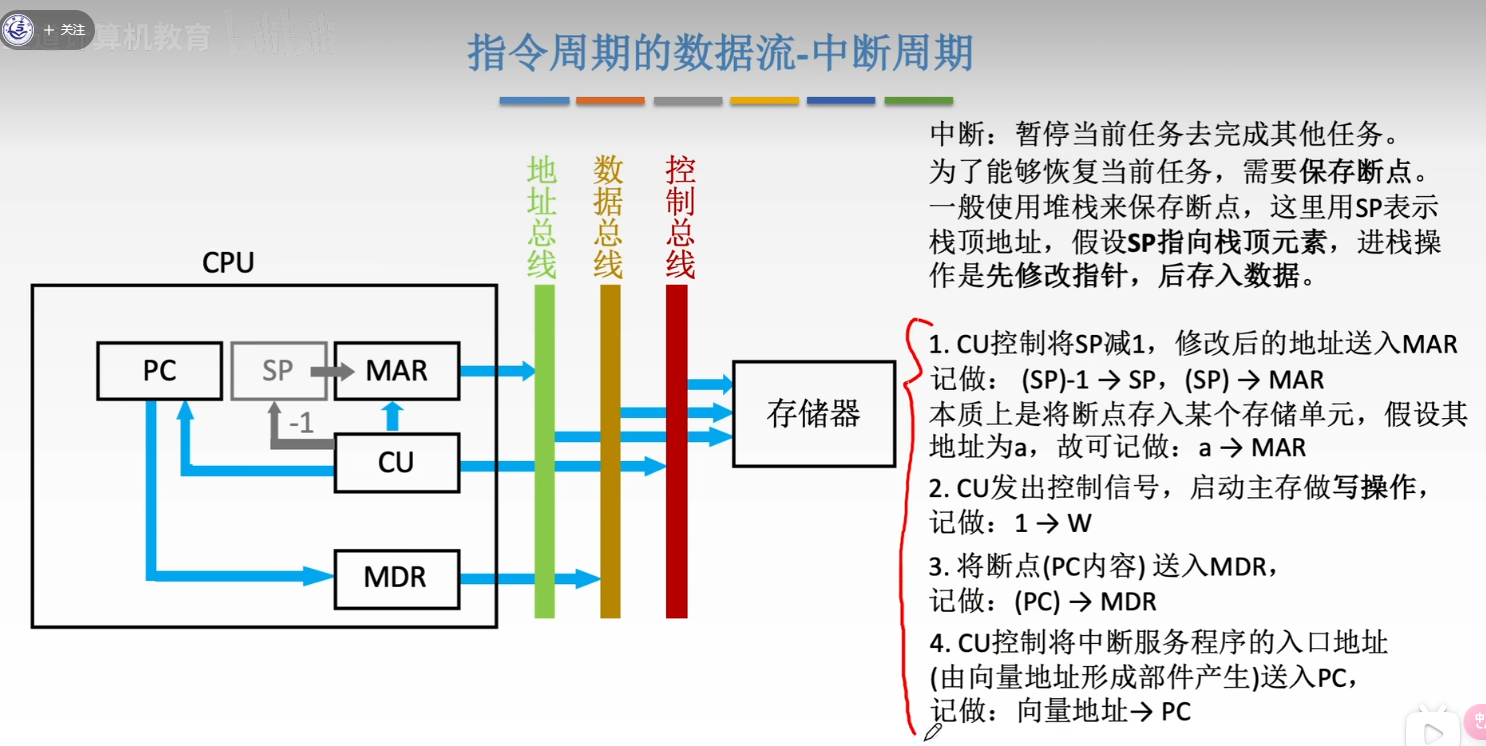

5.中断周期

中断周期是指计算机在执行过程中遇到中断请求时,保存当前执行状态,转移到中断服务程序处理中断,完成后恢复原来执行状态的过程。

6.存储周期(Memory Access Cycle)

如果指令需要,对存储器进行读/写操作。

7.写回周期(Write-back Cycle)

将结果写回到寄存器或内存中。

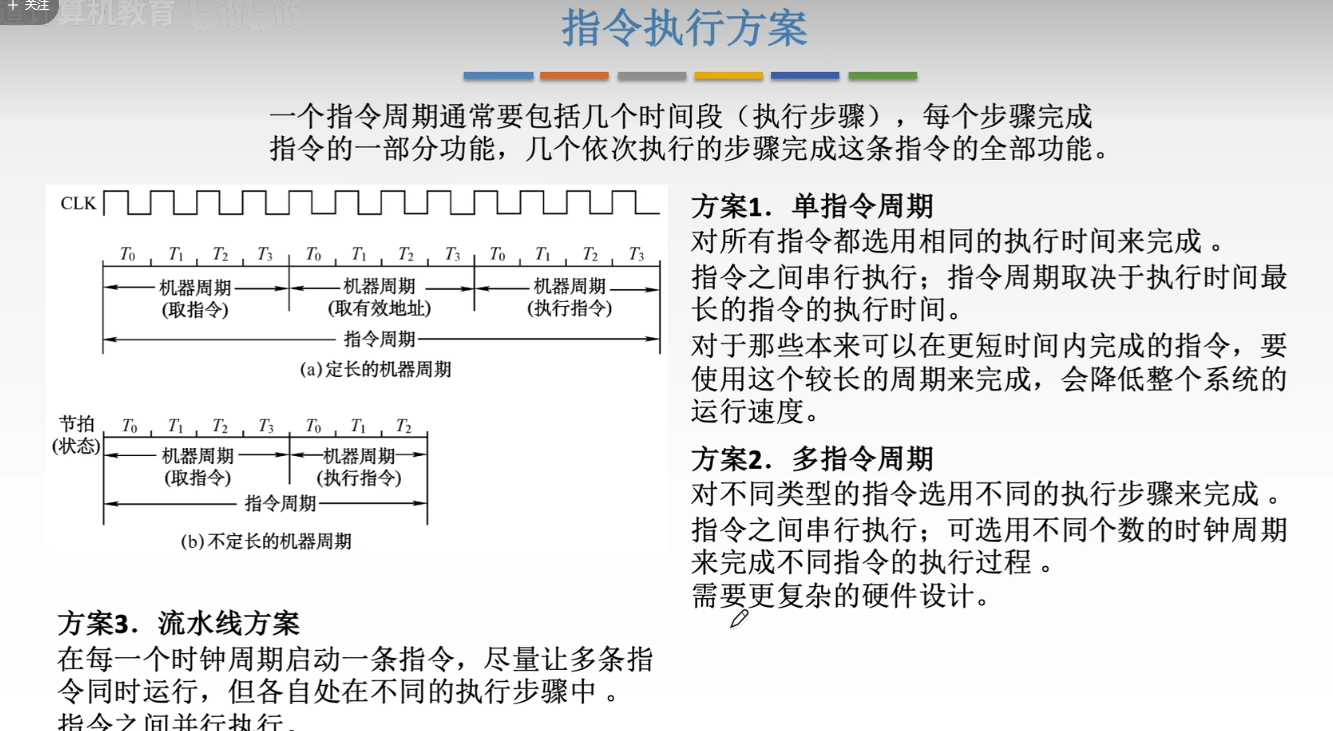

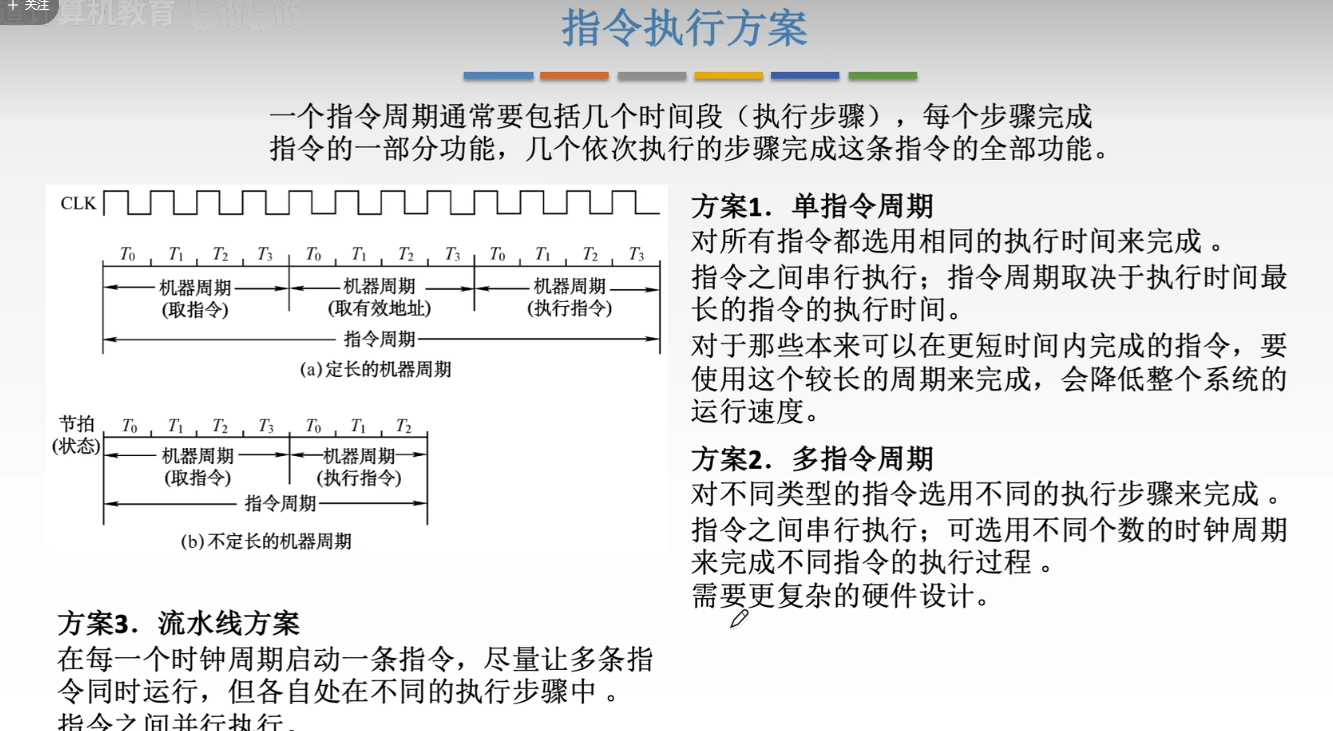

结构形式

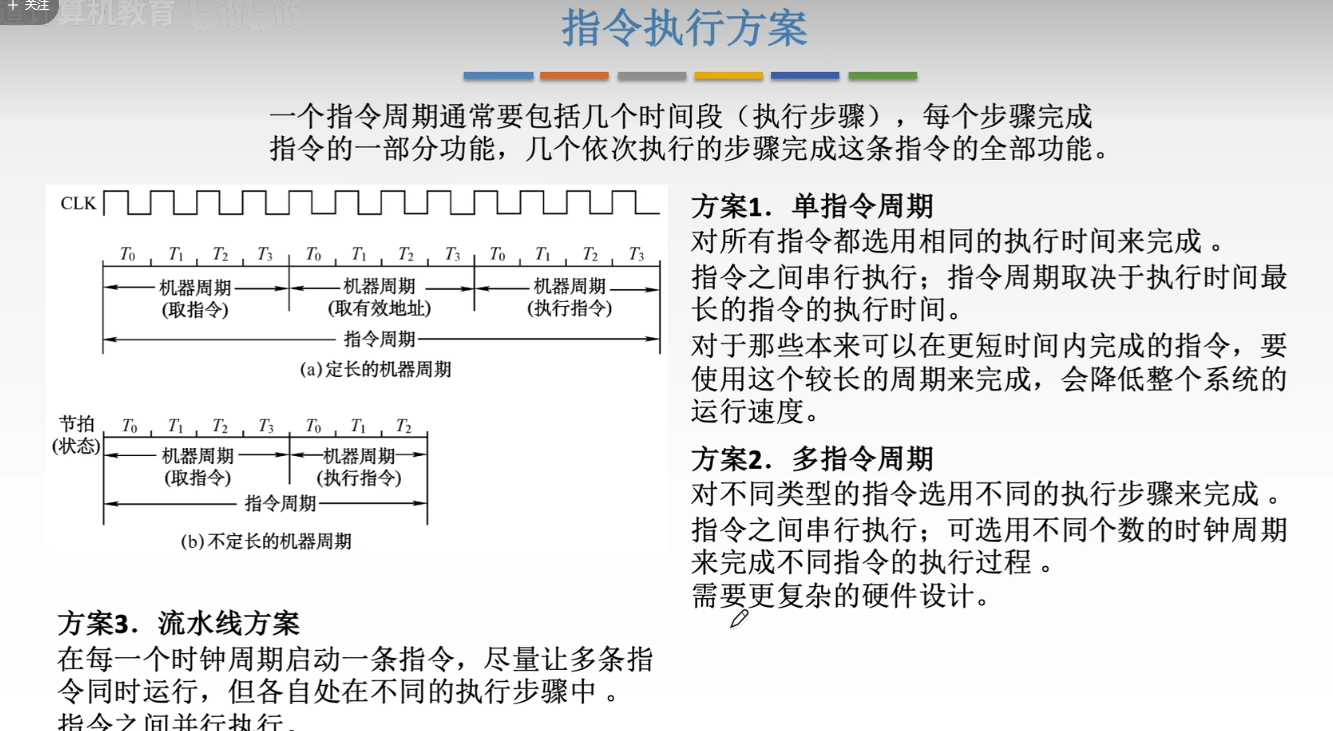

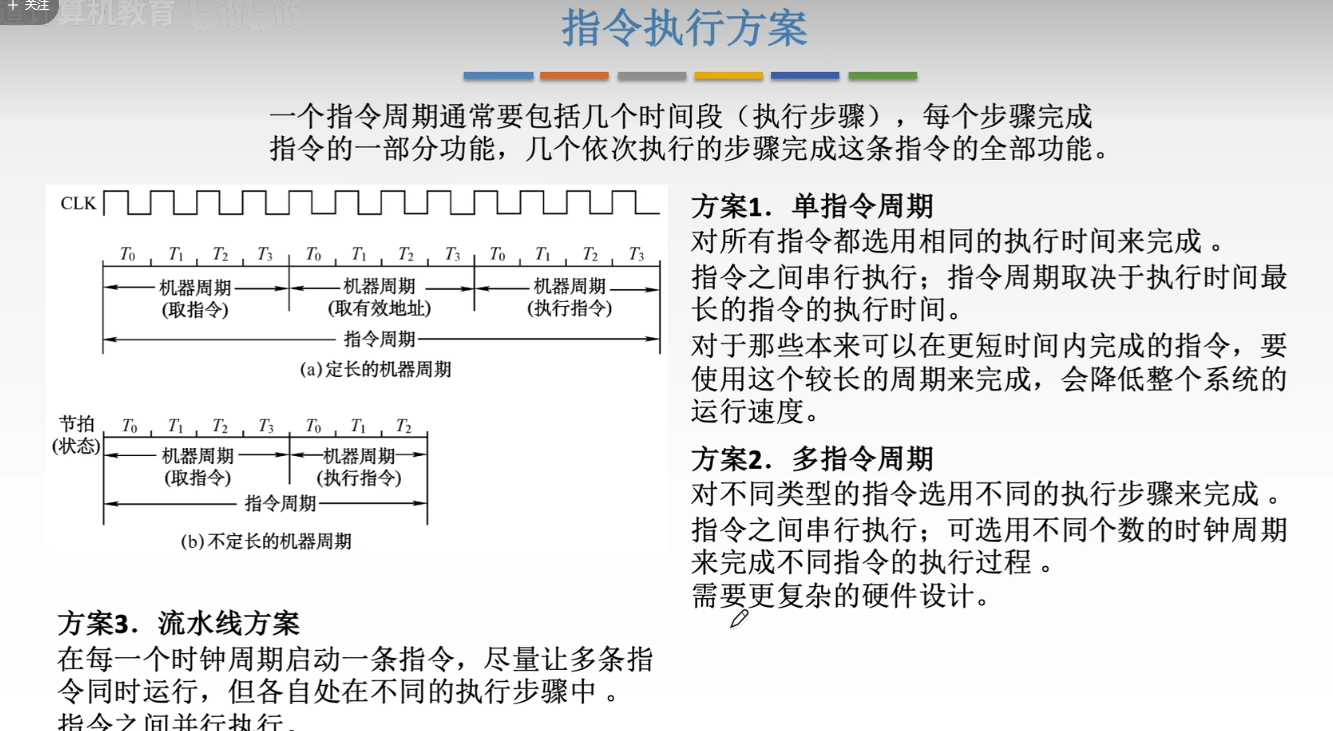

1.非流水线结构

各步骤顺序执行,一次处理一条指令。

2.流水线结构

将指令周期的各步骤重叠执行,提高指令处理效率。

分类

1.RISC(精简指令集计算机)

指令周期通常较短,指令集简单。

2.CISC(复杂指令集计算机)

指令周期较长,指令集复杂。

特征

1.阶段性:指令周期由若干固定阶段组成。

2.数据流动:数据在指令周期内在CPU和内存之间传递。

3.控制信号:控制单元生成的控制信号指示各阶段的操作。

使用方法

目的

通过描述指令周期,理解CPU内部指令执行过程,提高程序设计和优化能力。

基本原理

周期

定义

指令周期是计算机执行一条指令所经历的整个过程,从取出指令到完成指令执行,包括所有的步骤和阶段。每条指令的执行都需要经历若干个固定的步骤,这些步骤构成了指令周期。

组成部分

1.取指周期(Fetch Cycle)

从内存中取出指令。

2.译码周期(Decode Cycle)

将取出的指令译码,以确定操作类型和操作数。

3.间址周期(Indirect Cycle)

如果指令使用间接地址方式,需要访问内存获取实际操作数地址。

4.执行周期(Execute Cycle)

执行指令所规定的操作。

5.中断周期

中断周期是指计算机在执行过程中遇到中断请求时,保存当前执行状态,转移到中断服务程序处理中断,完成后恢复原来执行状态的过程。

6.存储周期(Memory Access Cycle)

如果指令需要,对存储器进行读/写操作。

7.写回周期(Write-back Cycle)

将结果写回到寄存器或内存中。

结构形式

1.非流水线结构

各步骤顺序执行,一次处理一条指令。

2.流水线结构

将指令周期的各步骤重叠执行,提高指令处理效率。

分类

1.RISC(精简指令集计算机)

指令周期通常较短,指令集简单。

2.CISC(复杂指令集计算机)

指令周期较长,指令集复杂。

特征

1.阶段性:指令周期由若干固定阶段组成。

2.数据流动:数据在指令周期内在CPU和内存之间传递。

3.控制信号:控制单元生成的控制信号指示各阶段的操作。

使用方法

目的

通过描述指令周期,理解CPU内部指令执行过程,提高程序设计和优化能力。

基本原理

# 指令周期

# 指令周期

定义

指令周期是计算机执行一条指令所经历的整个过程,从取出指令到完成指令执行,包括所有的步骤和阶段。每条指令的执行都需要经历若干个固定的步骤,这些步骤构成了指令周期。

组成部分

1.取指周期(Fetch Cycle)

从内存中取出指令。

2.译码周期(Decode Cycle)

将取出的指令译码,以确定操作类型和操作数。

3.间址周期(Indirect Cycle)

如果指令使用间接地址方式,需要访问内存获取实际操作数地址。

4.执行周期(Execute Cycle)

执行指令所规定的操作。

5.中断周期

中断周期是指计算机在执行过程中遇到中断请求时,保存当前执行状态,转移到中断服务程序处理中断,完成后恢复原来执行状态的过程。

6.存储周期(Memory Access Cycle)

如果指令需要,对存储器进行读/写操作。

7.写回周期(Write-back Cycle)

将结果写回到寄存器或内存中。

结构形式

1.非流水线结构

各步骤顺序执行,一次处理一条指令。

2.流水线结构

将指令周期的各步骤重叠执行,提高指令处理效率。

分类

1.RISC(精简指令集计算机)

指令周期通常较短,指令集简单。

2.CISC(复杂指令集计算机)

指令周期较长,指令集复杂。

特征

1.阶段性:指令周期由若干固定阶段组成。

2.数据流动:数据在指令周期内在CPU和内存之间传递。

3.控制信号:控制单元生成的控制信号指示各阶段的操作。

使用方法

目的

通过描述指令周期,理解CPU内部指令执行过程,提高程序设计和优化能力。

基本原理

周期

定义

指令周期是计算机执行一条指令所经历的整个过程,从取出指令到完成指令执行,包括所有的步骤和阶段。每条指令的执行都需要经历若干个固定的步骤,这些步骤构成了指令周期。

组成部分

1.取指周期(Fetch Cycle)

从内存中取出指令。

2.译码周期(Decode Cycle)

将取出的指令译码,以确定操作类型和操作数。

3.间址周期(Indirect Cycle)

如果指令使用间接地址方式,需要访问内存获取实际操作数地址。

4.执行周期(Execute Cycle)

执行指令所规定的操作。

5.中断周期

中断周期是指计算机在执行过程中遇到中断请求时,保存当前执行状态,转移到中断服务程序处理中断,完成后恢复原来执行状态的过程。

6.存储周期(Memory Access Cycle)

如果指令需要,对存储器进行读/写操作。

7.写回周期(Write-back Cycle)

将结果写回到寄存器或内存中。

结构形式

1.非流水线结构

各步骤顺序执行,一次处理一条指令。

2.流水线结构

将指令周期的各步骤重叠执行,提高指令处理效率。

分类

1.RISC(精简指令集计算机)

指令周期通常较短,指令集简单。

2.CISC(复杂指令集计算机)

指令周期较长,指令集复杂。

特征

1.阶段性:指令周期由若干固定阶段组成。

2.数据流动:数据在指令周期内在CPU和内存之间传递。

3.控制信号:控制单元生成的控制信号指示各阶段的操作。

使用方法

目的

通过描述指令周期,理解CPU内部指令执行过程,提高程序设计和优化能力。

基本原理